## 以FPGA T SOC 為基礎設計 一防止風力發電系統孤島運轉で保護電驛

# Design of a FPGA-based SOC Relay for Anti-islanding Protection on Wind Power Generation Systems

國立台灣科技大學電機系教授 辜 志承國立台灣科技大學電機系 許家榮

#### 摘要

本文以基於 FPGA 的系統晶片(SOC) 設計方式,開發適用於風力發電系統之被 動式孤島運轉保護電驛,軟體方面包含過 電流、過/欠電壓、過/欠頻率、頻率變化 率、相位跳躍、逆電力、複合電壓變化率 及功因變動等孤島偵測演算法則之撰寫, 硬體方面則建構各演算法則之矽智產 (Intellectual Property, IP)、ADC、週邊介 面控制 IP 與加入現行可用之 IP,經過整 合並完成 SOC 孤島運轉保護電驛之製 作。最後應用 Matlab/Simulink 模擬 IEEE Std.1547.1、IEEE Std.929 及 UL 1741 所 建議之孤島運轉測試電路與方法,其數位 模擬結果再藉由 doble 電驛試驗器輸出對 應之類比訊號進行 SOC 孤島運轉保護電 驛之測試,由實測結果可知,本電驛可有 效防範風力發電系統孤島運轉現象之發 生。

關鍵詞:孤島運轉、數位保護電驛、矽智 產、風力發電系統、FPGA、 SOC

#### 一、前言

孤島運轉係指當分散型電源 (Distributed Generation, DG)與市電系統併 聯運轉時,如市電系統供電因故中斷,而 DG 並未及時檢知且持續供電,造成部份配電系統仍有單獨受電的狀況。當發生孤島運轉時,將會造成許多不良的影響,例如:市電故障後,電力維修人員必須在斷電的情況下將市電的故障修復排除,但此時 DG 仍維持供電,將危害到電力維修人員的安全;另外孤島運轉期間,電壓及頻率不穩定,用電設備亦容易損壞[1-3]。

孤島運轉偵測技術可分為遠端偵測與 本地偵測。遠端偵測係以通訊系統為基 礎,藉由 DG 與市電系統相互傳送信號並 確認雙方的運作狀況或利用監控市電系統 之斷路器或開關狀態,進而判斷是否跳脫 DG,使其停止供電;本地偵測又分為主 動式方法與被動式方法。主動式方法主要 在市電系統中加入一微量擾動信號,正常 運轉情況下,此一擾動並未對系統造成任 何變化與影響,當孤島運轉發生時,此一 擾動將使得系統的狀態改變,藉由監視系 統的狀態變化,來判斷孤島運轉之發生; 被動式方法主要以監控市電系統之相關電 力量,如電壓或頻率等變化為依據,當偵 測之電力量發生明顯變化,並超過相關運 轉規範時,將跳脫 DG 使其與系統解聯 [4]。

遠端偵測方法雖無偵測不感帶(Nondetection Zone, NDZ),但其需裝設通訊設備,將使得設置成本大幅增加,而當 DG

位處於偏遠地區時,還需考慮裝設困難度 等問題,且對於監視 DG 端之數個斷路器 狀態也將增加系統的複雜度。主動式方法 雖為有效的孤島偵測方式,但其必須不斷 的改變 DG 之輸出狀態,可能使 DG 本身 與市電系統產生不良的影響。一般被動式 方法之 NDZ 比主動式與遠端方法大,但 隨著許多新的被動式偵測技術被提出, NDZ 也逐漸的被縮小,且其製作簡單及 成本較低,非常適合應用在風力發電系統 之孤島運轉偵測[4]。

本文以 FPGA 的系統晶片(System On a Chip, SOC)為基礎製作孤島運轉偵測電驛,其有體積小、可靠度高、保密性高及開發週期短與上市利機快等優點,並導入矽智產(IP)可重複使用的觀念, IP 為使用硬體描述語言事先撰寫好且已經過驗證的

功能模組,利用現成可用的 IP 來對電驛作設計,可縮短開發時間與減少開發成本 [5,6]。本電驛整合多種被動式偵測方法,提供一個多功能保護之孤島運轉解決方案。

#### 二、孤島保護電驛之系統晶片設計

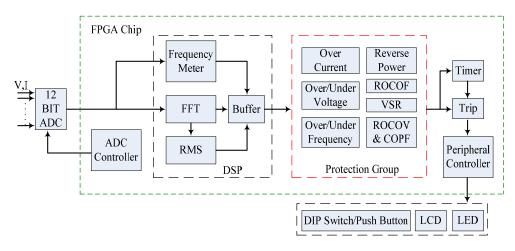

保護電驛之系統晶片架構,如圖 1 所示,主要包含三大部份:(1)數位信號處理模組(Digital Signal Processor, DSP),(2)類比數位轉換器(Analog to Digital Converter, ADC)與週邊介面控制(Peripheral Controller) IP 及(3)保護群組(Protection Group)。為集合計算、控制與保護於單一顆 FPGA 晶片的多功能孤島偵測電驛系統晶片。

圖 1 孤島保護電驛之系統晶片

本文使用 Xilinx ISE 中免費 IP 資料庫(CORE Generator)所提供的快速傅立葉轉換(Fast Fourier Transform, FFT) IP,作為電驛的主要運算核心。採用 radix-4 64點分時 FFT 架構計算 ADC 所取樣的電壓與電流信號,運算結果可得信號之基頻成份與 2 到 32 階之諧波成份。另外,利用一高速的計數器可量測電壓信號之頻率

$(f_{in})$ ,如公式(1)所示[7],其中  $f_c$ 為計數器 頻率,n 為相對應之計數值;各階成份之 有效值 $(X_{rms}(n))$ 與相角 $(X_{\angle\theta}(n))$ 計算如公式 (2)與(3)所示,其中  $xk_{re}(n)$  為各階成份之實部,  $xk_{im}(n)$  為各階成份之虛部。整合 FFT IP、頻率量測 (Frequency Meter) IP 與 RMS IP 成為 DSP 計算模組。

$$f_{in} = \frac{f_c}{2n} \tag{1}$$

$$X_{rms}(n) = \frac{2}{N\sqrt{2}} * \sqrt{xk_{re}(n)^2 + xk_{im}(n)^2}$$

(2)

$$X_{\angle \theta}(n) = \tan^{-1} \frac{x k_{im}(n)}{x k_{r_{e}}(n)}$$

(3)

本文使用 Xilinx 公司出產之 Spartan-3 MB 開發板,並擴充一組 ADC 對電壓 與電流信號作取樣,為 12 位元資料精度 且取樣頻率最高可至 53 Msps, ADC 控 制 IP 可對其作初始設定與設定取樣頻率 等;週邊介面控制 IP 主要為開發版之 LCD 顯示器驅動及開關或按鈕的動作設 定。

針對目前文獻中所提及之被動式孤島 偵測方法,包括過電流、過/欠電壓、過/ 欠頻率、頻率變化率(ROCOF)、相位跳躍 (VSR)、逆電力、複合電壓變化率及功因 變動,使用 Verilog 硬體描述語言建構各 型電驛 IP 並整合為一個保護群組。電驛 IP 使用 ModelSim 軟體作功能與時序模 擬,且要求行為模擬(Behavioral Simulation)與後端模擬(Post Simulation)之結果一 致,以符合工業界的標準並確保電驛演算 法的正確性。

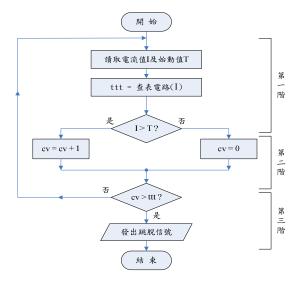

過電流電驛為監視 DG 當發生過載、 短路等過電流事故時,跳脫斷路器使其與 系統解聯。過電流電驛 IP 之動作流程如 圖 2 所示,採用三階管線架構,第一階之 動作為將輸入電流值(I)送至查表電與 相對應的延遲時間(ttt),同時將 I 與始 值(T)相比較,如發生過電流,則過電流 信號(fc)為高電位;反之,為低電位 開始計數,計數值為(cv);反之,cv 設為 Cv 共於 ttt,則發出跳脫信號(高電位);反 之,則為低電位[8]。

DG 與市電系統併聯運轉時,如市電

電源因故切離時,負載功率轉由 DG 來提供,如市電所提供之功率不為零,PCC點電壓將因此改變,過/欠電壓電驛可偵測此一改變並防止孤島運轉發生。過/欠電壓電驛 IP 之建構仿照過電流電驛之三階管線架構,只需將輸入電流(I)換成輸入電壓(V)及查表電路換成是儲存電壓與對應之跳脫時間(V-t 曲線)即可。

圖 2 過電流電驛 IP 之動作流程圖

在 DG 設備中設置過/欠頻率電驛,當頻率超過設定上限或低於設定下限時,立刻跳脫 DG,確保設備安全及防止孤島運轉發生。頻率的估算如公式(1),求得頻率後,設定跳脫的保護區間,即可完成過/欠頻率電驛 IP 之建構。

當市電電源切離時,負載功率轉由 DG 來提供,如市電所提供之功率不為 零,PCC 點電壓在相位上有一快速之改 變,電壓之瞬間值將跳躍至另一數值,利 用 VSR 可偵測電壓波形的變化,判斷孤 島運轉之發生。依據孤島電力不足或 多,每個週期的時間可能變長或變知而 頻率也跟著變大或變小,每週時間之變化 量正比於電壓角度之變化,當電壓之角度 變化量超過相位跳躍電驛之設定值時(一 般為 2°~20°),則發出跳脫信號。

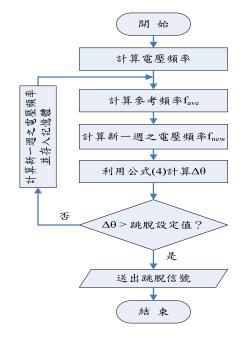

圖 3 為 VSR IP 之動作流程圖,首先 計算輸入電壓之頻率,接著連續儲存 8 筆 頻率值於電驛內部之記憶體中並計算出此 8 筆頻率之平均頻率 fave,再求得下一週 之頻率值 fnew,由公式(4)估算相角變化值 Δθ,判斷 Δθ 是否大於跳脫設定值,如超 過,則發出跳脫信號;反之,則求出下一 週之電壓頻率值並移除原本記憶體 8 筆中 最舊一筆頻率,存入最新一筆計算之頻 率,再重複上述之計算流程[2]。

$$\Delta\theta = \frac{\frac{1}{f_{new}} - \frac{1}{f_{ave}}}{\frac{1}{f_{mew}}} \times 360^{\circ}$$

$$\tag{4}$$

圖 3 相位跳躍電驛 IP 之動作流程圖

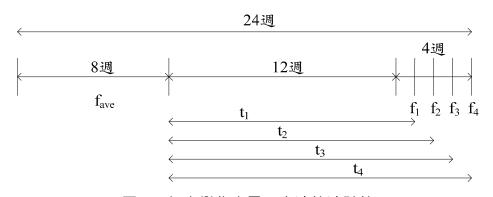

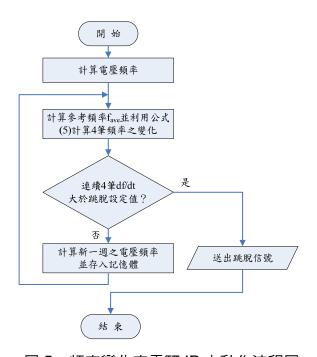

孤島現象產生時,頻率會因實功率的 不平衡而變動的非常快速,使用 ROCOF 偵測頻率的變化程度,一旦超過跳脫設定 值(以一般 60 Hz 系統而言,典型設定值 為 0.1~1.2 Hz/sec), 將跳脫 DG 防止孤島 運轉的發生。ROCOF 另一重要的特性是 低電壓閉鎖功能,當DG端電壓低於某一 設定值V<sub>min</sub> 時,則電驛所送出之跳脫命令 將被閉鎖。ROCOF 之演算法計算通常考 慮幾個週期的量測視窗,一般為 2~50 週,如此可提升其運算的精確度,如圖 4 所示,使用一組可連續儲存 24 週頻率值 的記憶體,以前8週(視窗一)取平均並作 為參考頻率 fave, 然後計算 12 週(視窗二) 後連續 4 筆頻率相對於參考頻率 fave 之頻 率變化,如連續4筆頻率變化大於設定值 時,則發出跳脫信號。

圖 5 為 ROCOF IP 之動作流程圖,開始計算輸入電壓之頻率,接著連續儲存 24 筆頻率值於電驛內部之記憶體中並計算出參考頻率 fave,再由公式(5)求得第 20 筆後連續 4 筆頻率相對於 fave 之頻率變化,接著判斷 4 筆頻率變化值(fi)是否大於跳脫設定值,如超過,則發出跳脫信號;反之,則求出下一週之電壓頻率值並移除原本記憶體 24 筆中最舊一筆頻率,存入最新一筆計算之頻率,再重複上述之計算流程[2]。

圖 4 頻率變化率電驛之演算法計算

$$\frac{df}{dt} = \frac{f_i - f_{ave}}{dt} \tag{5}$$

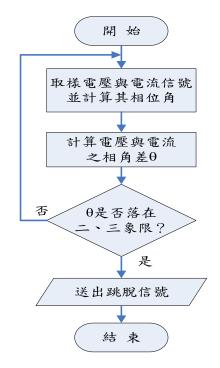

逆電力電驛在互聯點(Inter-tie)上監視 DG 之電力潮流方向,可防止逆送電力至市電網路,防範孤島運轉的產生。圖 6 為逆電力電驛 IP 之動作流程,首先計算電壓及電流基本波之相位角,接著再計算電壓與電流之間的相角差  $\theta$ ,判斷  $\theta$  是否落於二、三象限(即  $\cos\theta < 0$ ),如無,由 $P=VI\cos\theta$ ,P>0 無逆送電力,電驛發出跳脫信號。

圖 5 頻率變化率電驛 IP 之動作流程圖

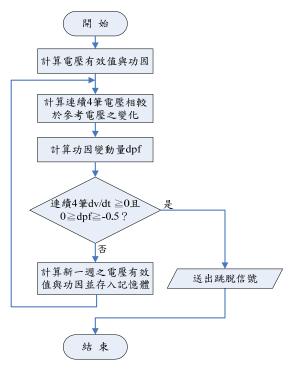

當孤島現象發生時,在 PCC 點上的電壓變化會明顯的大於在正常運轉時的狀態,藉由偵測此電壓變化,以防止孤島現象發生,且為了避免因市電系統的種種擾動(如電容器的切換導致電壓變動等)使得電驛產生誤動作,加入對功率因數的變動價測,即為電壓變化率及功因變動電驛,傾測孤島現象發生更為準確並減少電驛誤動作的機會。其偵測的保護跳脫邏輯如公式(6)所示,當

電壓變化率大於零(即 A=1)且功因變動落在 0 與-0.5 之間(即 B=1)時,電驛判斷為孤島現象發生並發出跳脫信號[9]。

圖 6 逆電力電驛 IP 之動作流程圖

Trip = A • B

其中

$$A = \begin{cases} 1, & \triangleq \frac{dV}{dt} \ge 0 \\ 0, & \text{ i.e.} \end{cases} \quad B = \begin{cases} 1, & \triangleq 0 \ge \Delta pf \ge -0.5 \\ 0, & \text{ i.e.} \end{cases}$$

電壓變化率製作上與 ROCOF 之架構類似,利用一組可連續儲存 24 週電壓之記憶體,前 8 週資料取平均並作為參考電壓,接著計算 12 週後連續 4 筆電壓一條 4 筆電壓變化,如連續 4 筆電壓變化,如連續 4 筆電壓變化。如連續 4 筆電壓變化。如連續 4 筆電壓變化。如連續 4 筆電壓變化率之跳脫信號為高電位。功率因數之計算方法為求出電壓與電流間之相角差後,經由餘弦(cos)查表電對應後即可求得,使用一組的功因值,其值為 dpf,如付方落在 0~-0.5 之間,則功因變動之跳脫信號為高電位。當電壓變化率之跳脫信號

與功因變動之跳脫信號均為高電位時,才 會送出輸出真正的跳脫信號,動作流程 圖,如圖7所示。

圖 7 電壓變化率及功因變動電器 IP 之動作流程圖

### 三、孤島電驛測試

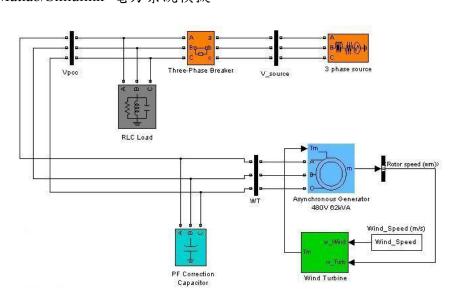

使用 Matlab/Simulink 電力系統模擬

軟體建立於 IEEE 1547.1[10]、UL 1741[11]與 IEEE 929[12]之孤島運轉測試 電路,如圖 8 所示,待測設備(Equipment Under Test, EUT)使用感應發電機型式之 風力發電機,風力機模型利用查表法 (Wind Turbine 模塊)建構其特性曲線圖, 於不同的風速下,可得不同之輸出功率, 功因校正電容器(PF Correction Capacitor) 為風力機之虛功補償電容;負載為 RLC 負載;三相斷路器(Three Phase Breaker)用 於切斷市電電源(Three Phase Source),以 製造孤島運轉現象發生。本文依據測試方 法,設定測試電路之品質因數為 2.5,且 風力機有三種輸出功率情況,分別為 25%、50%與 100%之風機額定輸出功 率,且在每種輸出功率情況下,調整測試 電路中電感性負載之虛功率 Pal,每次以 1%的增加率遞增,使 P<sub>qL</sub> 由 95%~105%變 化,總計 11 種測試狀況。此測試電路模 擬時間為 3.5 秒,三相斷路器於 1 秒時打 開,由圖 8 中 Vpcc 點取得模擬之三相電 壓與電流波形,作為孤島保護電驛測試之 輸入波形。

圖 8 孤島運轉模擬測試電路

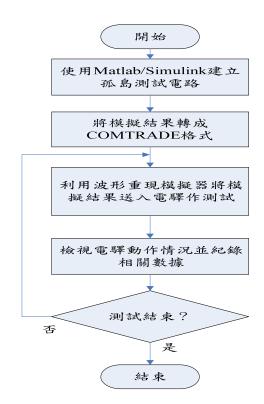

圖 9 為孤島保護電驛之測試流程,首 先依據標準建立孤島測試電路,模擬風力 機與負載形成孤島運轉,得出風力機輸出 端之三相電壓與電流時域波形,將波形轉 換為 IEEE COMTRAD 資料格式後,再利 用 Doble 電驛試驗器將這些波形送入電驛 作測試,檢視電驛動作情形並依電驛動作 情況微調電驛之相關參數設定,以確保電 驛動作之正確性。

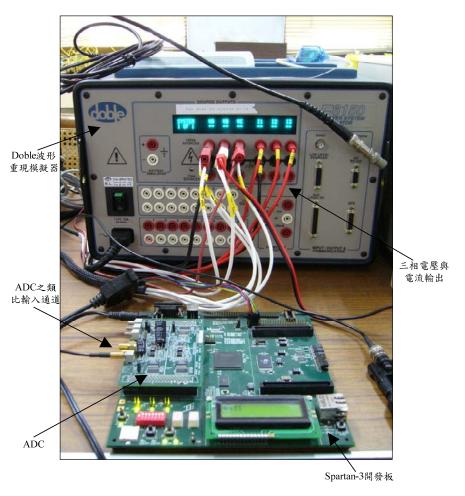

電驛實際接線測試如圖 10 所示,將Doble 面板上之電壓與電流輸出通道接至Spartan-3 MB 開發板上之 ADC 類比輸入通道,波形送入電驛後,電驛開始作偵測的動作。當偵測出孤島運轉發生時,即發出跳脫信號,開發板上之跳脫 LED 燈會亮起,且 LCD 模組會顯示跳脫的時間。

圖 9 孤島保護電驛之測試流程圖

圖 10 孤島電驛開發板接線測試圖

開發板上孤島保護電驛 IP 選擇 ROCOF 與 VSR 雙重保護組合,跳脫信號為兩者或閘(OR)後輸出。風力機輸出分別於 100%、50%與 25%額定輸出功率,且負載消耗虚功率(PqL)由 95%~105%變化之電驛偵測跳脫時間,如表 1、2 與3 所示。每個測試狀況總共測試 10 次,並列出平均跳脫時間、最大跳脫時間與東小跳脫時間,由表可知,本電驛能別,由表可知,本電驛能別時間(2 秒內)偵測出孤島運轉現象,除了在風力機輸出功率與負載消耗功率幾乎匹配情況下(PqL於 100%情況),本電驛無法偵測出來,這是可以被預期的,因其為被動式孤島保護電驛之 NDZ 範圍。

表 1 風力機於 100%額定輸出且負載虛功由 95%~105%變化下之孤島電 瞬偵測跳脫時間表

| P <sub>qL</sub> (%) | 測試次數(次) | 平均跳脫時間(秒) | 最大跳脫<br>時間(秒) | 最小跳脫<br>時間(秒) |

|---------------------|---------|-----------|---------------|---------------|

| 95%                 | 10      | 0.736     | 1.016         | 0.610         |

| 96%                 | 10      | 0.918     | 1.184         | 0.778         |

| 97%                 | 10      | 0.589     | 1.198         | 0.232         |

| 98%                 | 10      | 0.620     | 0.778         | 0.372         |

| 99%                 | 10      | 0.702     | 0.876         | 0.484         |

| 100%                | 10      | No Trip   | No Trip       | No Trip       |

| 101%                | 10      | 0.740     | 0.890         | 0.652         |

| 102%                | 10      | 0.617     | 0.778         | 0.428         |

| 103%                | 10      | 0.828     | 0.974         | 0.708         |

| 104%                | 10      | 0.541     | 0.876         | 0.204         |

| 105%                | 10      | 0.653     | 0.764         | 0.540         |

開發板上孤島保護電驛 IP 選擇 表 2 風力機於 50%額定輸出且負載虚 OF 與 VSR 雙重保護組合, 跳脫信 功由 95%~105%變化下之孤島電 兩者或閱(OR)後輸出。風力機輸出 驛偵測跳脫時間表

| 疑                   |             |               |               |           |  |  |  |

|---------------------|-------------|---------------|---------------|-----------|--|--|--|

| P <sub>qL</sub> (%) | 測試次<br>數(次) | 平均跳脫<br>時間(秒) | 最大跳脫<br>時間(秒) | 最小跳脫時間(秒) |  |  |  |

| 95%                 | 10          | 0.568         | 0.778         | 0.344     |  |  |  |

| 96%                 | 10          | 0.775         | 0.904         | 0.428     |  |  |  |

| 97%                 | 10          | 0.501         | 0.680         | 0.218     |  |  |  |

| 98%                 | 10          | 0.565         | 0.750         | 0.134     |  |  |  |

| 99%                 | 10          | 0.683         | 0.946         | 0.428     |  |  |  |

| 100%                | 10          | No Trip       | No Trip       | No Trip   |  |  |  |

| 101%                | 10          | 0.627         | 1.044         | 0.204     |  |  |  |

| 102%                | 10          | 0.491         | 0.554         | 0.302     |  |  |  |

| 103%                | 10          | 0.616         | 0.960         | 0.232     |  |  |  |

| 104%                | 10          | 0.506         | 0.582         | 0.372     |  |  |  |

| 105%                | 10          | 0.539         | 0.806         | 0.092     |  |  |  |

表 3 風力機於 25%額定輸出且負載虚功由 95%~105%變化下之孤島電 驛偵測跳脫時間表

| 降很别此脱时间衣            |         |               |               |               |  |  |  |

|---------------------|---------|---------------|---------------|---------------|--|--|--|

| P <sub>qL</sub> (%) | 測試次數(次) | 平均跳脫<br>時間(秒) | 最大跳脱<br>時間(秒) | 最小跳脫<br>時間(秒) |  |  |  |

| 95%                 | 10      | 0.471         | 0.652         | 0.176         |  |  |  |

| 96%                 | 10      | 0.663         | 0.806         | 0.498         |  |  |  |

| 97%                 | 10      | 0.418         | 0.638         | 0.190         |  |  |  |

| 98%                 | 10      | 0.614         | 1.590         | 0.288         |  |  |  |

| 99%                 | 10      | 0.560         | 1.156         | 0.106         |  |  |  |

| 100%                | 10      | No Trip       | No Trip       | No Trip       |  |  |  |

| 101%                | 10      | 0.660         | 1.226         | 0.358         |  |  |  |

| 102%                | 10      | 0.474         | 0.764         | 0.064         |  |  |  |

| 103%                | 10      | 0.708         | 0.960         | 0.526         |  |  |  |

| 104%                | 10      | 0.637         | 0.834         | 0.442         |  |  |  |

| 105%                | 10      | 0.607         | 1.030         | 0.316         |  |  |  |

#### 四、結論

對於風力發電系統之孤島運轉偵測方 法而言,基於實作的難易度與成本的考量 上,採用被動式偵測方法是最符合目前實際狀況及經濟實惠的辦法,目前文獻中 於探討被動式之偵測技術有非常多種, 法,而本文整合這些被動式偵測技術, 提一個完整的被動式孤島偵測解決方案, 使用者可依據需求選擇偵測的方法或是將 不同的偵測方法組合來做保護,其有多保 護功能與高彈性等優點。

本文使用平台式 FPGA 發展板開發出一套應用於風力發電系統之被動式孤島 偵測電驛原型機,以矽智產(IP)模組再利 用的觀念,加入現行可用的 IP 來對系統 作設計,可加速開發的時間與減少開發成 本。製作的電驛 IP 包括過電流、過/欠電 壓、相位跳躍、過/欠頻率、頻率變化 率、逆電力、複合電壓變化率及功因變 動。各個電驛 IP 使用 Verilog-HDL 撰 寫,其為 IEEE 之標準,可跨不同公司之 設計平台使用。

本文之孤島電驛測試部分,偵測方法 選用頻率變化率與相位跳躍電驛之組合來 做保護,兩者中只要有一者偵測出孤島現 象,即發出跳脫信號,電驛之測試信號來 源依據 UL 1741(IEEE Std.929)與 IEEE Std.1547.1 中之孤島運轉測試電路,模擬 得孤島運轉時風力機輸出端之三相電壓與 電流信號,透過波形重現模擬器即可將波 形送入電驛作測試,由跳脫時間表可知, 除了先天無法克服之 NDZ 範圍內無動作 外,均能於 2 秒內(IEEE Std.1547 所建議) 偵測出孤島現象發生。本電驛動作情況正 確,完成孤島電驛原型機的開發製作。

#### 五、參考文獻

- [1] 許時棋,「風力發電機併接於配電系 統孤島現象之研究」,國立台灣科技 大學碩士論文,民國95年1月。

- [2] 陳清山,羅天賜,「Vector Surge 及 ROCOF 孤島保護電驛之模擬分 析」,第 26 屆電力工程研討會,民 國 94 年 12 月 9 日。

- [3] 林保全,黃永福,羅天賜,「分散型 發電單獨運轉偵測保護技術」,電力 電子第2卷第4期,第38~45頁, 民國93年7月。

- [4] Jun Yin, Liuchen Chang, and Chris Diduch, "Recent Developments in Islanding Detection for Distributed Power Generation", IEEE Conference on Power Engineering, pp. 124-128, 28-30 July, 2004.

- [5] Zhang Guiqui, Feng Tao, Wang Jianhua, Zhang Hang, Xu Hong, Geng Yingsan, and Zheng Shiquan, "The SOC Design and Implementation of Digital Protective Relay Based on IP Cores", IEEE International Conference On Power System Technology, Vol. 4, pp. 2580-2583, Oct, 2002.

- [6] Zhang Guiqui, Feng Tao, Zhang Hang, Wang Jianhua, Xu Hong, Geng Yingsan, and Zheng Shiquan, "The Implementation of Digital Protection in Power System using FPGA", IEEE 4th International Conference on ASIC, pp. 474-477, Oct, 2001.

- [7] M. A. Manzoul, "Multi-function Protective Relay on FPGA", Microelectronics Reliability, 24 July, 1997.

- [8] M. A. Manzoul, and Prasad Modali,

- "Overcurrent Relay On a FPGA Chip", Microelectronics Reliability, Vol. 35, No. 7, pp. 1017-1022, 1995.

- [9] S. K. Salman, D. J. King, and G. Weller, "New Loss of Mains Detection Algorithm for Embedded Generation Using Rate of Change of Voltage and Changes in Power Factors", In IEE 7th International Conference on Developments in Power System Protection, pp. 82-85, 2001.

- [10] IEEE Std.1547.1, "IEEE Standard Conformance Test Procedures for Equipment Interconnecting Distributed

- Resources with Electric Power Systems", 1 July, 2005.

- [11] UL 1741, "Standard for Safety for Static Converters and Charge Controllers for Use in Photovoltaic Power Systems", 17 January, 2001.

- [12] IEEE Std.929, "IEEE Recommended Practice for Utility Interface of Photovoltaic (PV) Systems", 30 January, 2000.

- [13] IEEE Std.1547, "IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems", 28 July, 2003.